Xtremehardware

La nuova risorsa italiana di hardware e overclock

Xtremehardware

La nuova risorsa italiana di hardware e overclock

Recensioni su Processori - CPU

CPU

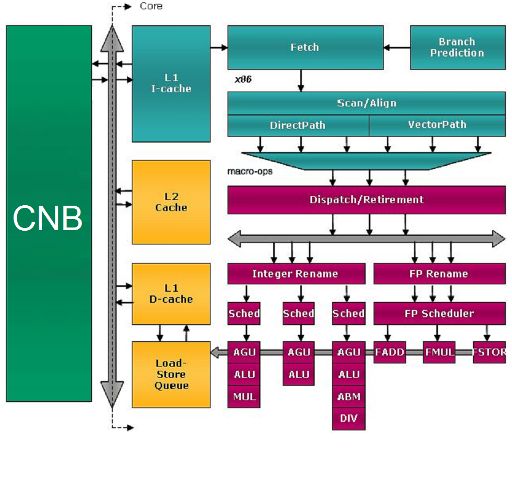

L’architettura del core Llano riprende e migliora quella dei core “Stars”, apportando alcune migliorie visibili fin dallo schema a blocchi.

Il blocco di colore verde, contiene il North Bridge, il controller per l’I/O del Chip e il controller RAM ed è indicato in figura con la dicitura CNB. Sarà descritto più avanti.

Il BUS grigio che si vede a fianco del CNB è il BUS di collegamento unico su cui si affacciano tutti i core e su cui sono abilitati a comunicare, a turno, dal NB.

Il resto del diagramma include uno dei core con le relative cache.

Tecniche di risparmio energetico

Dalla descrizione che segue nelle pagine successive, per chi conosce già la precedente architettura Stars, potrebbe sembrare che non sia poi cambiato molto. In realtà nel core Llano è stata implementata tutta una serie di tecniche avanzate di risparmio energetico.

Innanzitutto la griglia che distribuisce il clock è stata ridisegnata completamente e resa sparsa, ossia sono stati eliminati quei rami che non portavano il segnale a nessuna unità. Poi è stato implementato il clock gating alle varie unità e con un granularità molto spinta.

Il clock gating consiste nello spegnimento del clock a parti di un chip per ridurne sensibilmente il consumo.

Infine è stato introdotto lo stato di risparmio energetico CC6 che consiste nel togliere fisicamente l’alimentazione a tutto il core, tramite un anello di circa un milione di transistor attorno a ogni core.

E’ stato stimato da AMD che il risparmio di energia è pari al 16% in full load, del 36% in idle e oltre il 90% nello stato di risparmio energetico CC6, rispetto a un core Stars, normalizzando il consumo per il clock, per il processo produttivo e per il numero di transistor.

Ciò vuol dire che se il core Llano fosse stato realizzato con il processo produttivo a 45nm e avesse lo stesso numero di transistor di un core Stars, consumerebbe quanto indicato. E’ stato stimato, inoltre, che, normalizzando il consumo come detto precedentemente, in media, un core Llano consuma il 25% in meno.

Le differenze con il core Stars sono notevoli, soprattutto nello stato di risparmio energetico massimo, che non esiste nei core di vecchia generazione, in quanto un core in idle veniva portato a 800 o 1000 MHz, riducendo ma non azzerando il consumo. In particolare non c’era clock e power gating.

Tutto ciò era possibile grazie all’ottimo processo SOI che è stato ulteriormente migliorato, ma come possiamo vedere, con Llano si è ottenuto ancora di più, grazie all’introduzione di queste nuove tecnologie.

Tali tecniche sulla griglia del clock, sul clock e sul power gating sono state estese anche al North Bridge e soprattutto alla GPU, che beneficia anche del passaggio al processo 32nm HKMG SOI gate first di Global Foundries.

Come è visibile dall’immagine termica, gli anelli di transistor sono molto efficaci nel ridurre la dissipazione del calore. Senza di essi, ma con il solo clock gating, rimarrebbe il leakage, che nei processi SOI è molto basso, fino a 10-20 volte meno della concorrenza. Ma il processo 32nm HKMG SOI e gate first consente di usare nell’anello di transistor gli N-MOS, che sono in grado di ridurre di un ulteriore fattore 10 il già basso leakage.

La concorrenza invece usa un processo gate last, che richiede l’uso dei transistor P-MOS, meno efficaci, per il power gating. Risultato? Le parti spente non assorbono praticamente corrente, e rimangono quasi a temperatura ambiente. Un grande passo in avanti rispetto al core Stars.

Addentrandoci maggiormente nel funzionamento del risparmio energetico, possiamo dire che Llano ha due tensioni di alimentazioni separate: VDD e VDDNB. Sulla prima linea, sono collegati tutti i core, che quindi sono alimentati dalla stessa tensione. Sulla seconda linea sono collegate le restanti unità del chip: il Northbridge, la GPU, il blocco UVD e il blocco GIO.

Apparentemente potrebbe sembrare poco efficiente collegare tutti i core alla stessa tensione di alimentazione, perché il VDD deve essere pari alla tensione massima richiesta da tutti i core. Ma il clock gating spinto, il power gating spinto, lo stato CC6 per i core, il processo di litografia a bassissimo leakage e l’alta efficienza degli N-MOS di spegnimento dei core consentono un consumo quasi nullo per i core non utilizzati.

In realtà esistono due tipi di stato di risparmio energetico C6. Il CC6 (Core C6) è lo stato di risparmio energetico massimo di un singolo core, che abbiamo già visto. Ma se almeno un core è attivo, la tensione VDD e il generatore di clock non possono essere disattivati, consumando energia. Qui entra in gioco il secondo stato di risparmio energetico C6, più profondo, detto PC6 (package C6), che si attiva quanto tutti i core sono nello stato CC6. In questo caso sia la tensione di alimentazione che i clock dei core possono essere spenti, portando a un ulteriore risparmio.

Per quanto riguarda il VDDNB, anche qui un’unica tensione è un compromesso per ridurre la complessità di sistema, ma grazie sempre al clock gating e al power gating molto granulare, il risparmio energetico può essere consistente.

Come per i core, il VDDNB deve essere impostato alla tensione massima richiesta dai componenti alimentati. Il Northbridge ha i suoi P-State, così come la GPU, con il relativo controller di memoria, che è uno dei componenti dal maggior assorbimento e che per questo può essere spento indipendentemente dalla GPU, l’UVD e l’unità GIO (il P-State dipende dalla velocità dei link PCI Express, 1.0 o 2.0, che richiede tensione di alimentazione superiore).

Per quanto riguarda la GPU, essa può essere spenta automaticamente dall’hardware, tramite un timer programmabile da BIOS oppure dal driver grafico stesso. Ma come per i core, il clock gating e il power gating uniti al processo produttivo avanzato, consentono un consumo ottimale, come visibile nella immagine termica precedente.

Altre tecniche di risparmio energetico implementate, consistono nella compressione dei dati del frame buffer, che consente di trasferire meno dati e quindi risparmiare energia e una tecnica implementata nella versione mobile, chiamata adaptive backlight modulation (ABM), che consiste nel modulare la luminosità della lampada di retroilluminazione del display in funzione del contenuto visualizzato, per ridurne il consumo senza alterare in modo visibile le immagini visualizzate.